# Discipline & Good Practise of the ASIC/SoC Design Methodology

March 2019

Moscow

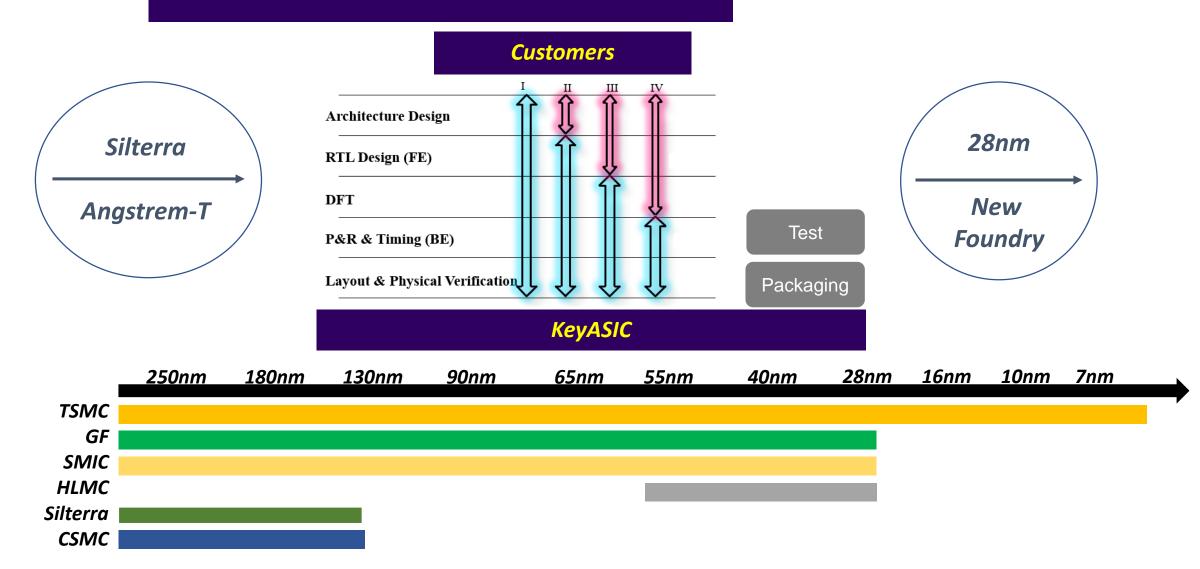

#### Capabilities

#### What else besides KNOWLEDGE?

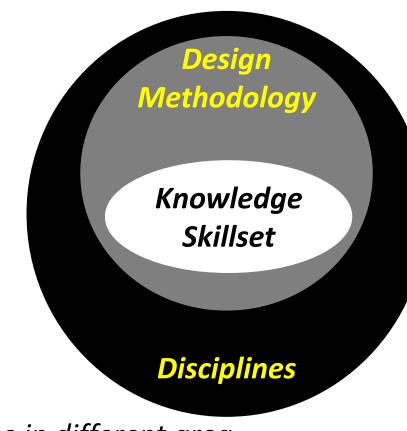

What is needed in designing an ASIC/SoC?

- Knowledge & skillset to design

- Establish competitive design methodology

- Discipline & Practice to execute/review (Attitude)

Methodology: A System of Methods that connect expertise in different area

What are the criteria of a competitive chip design methodology?

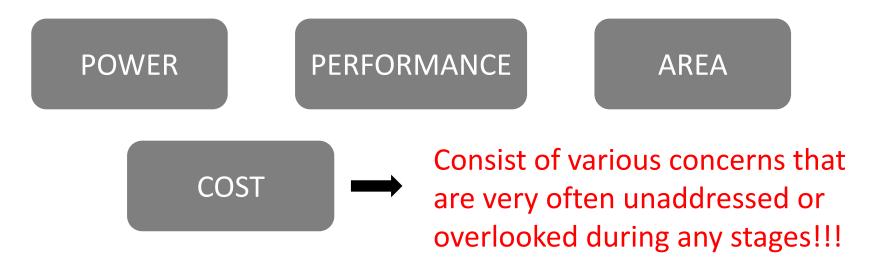

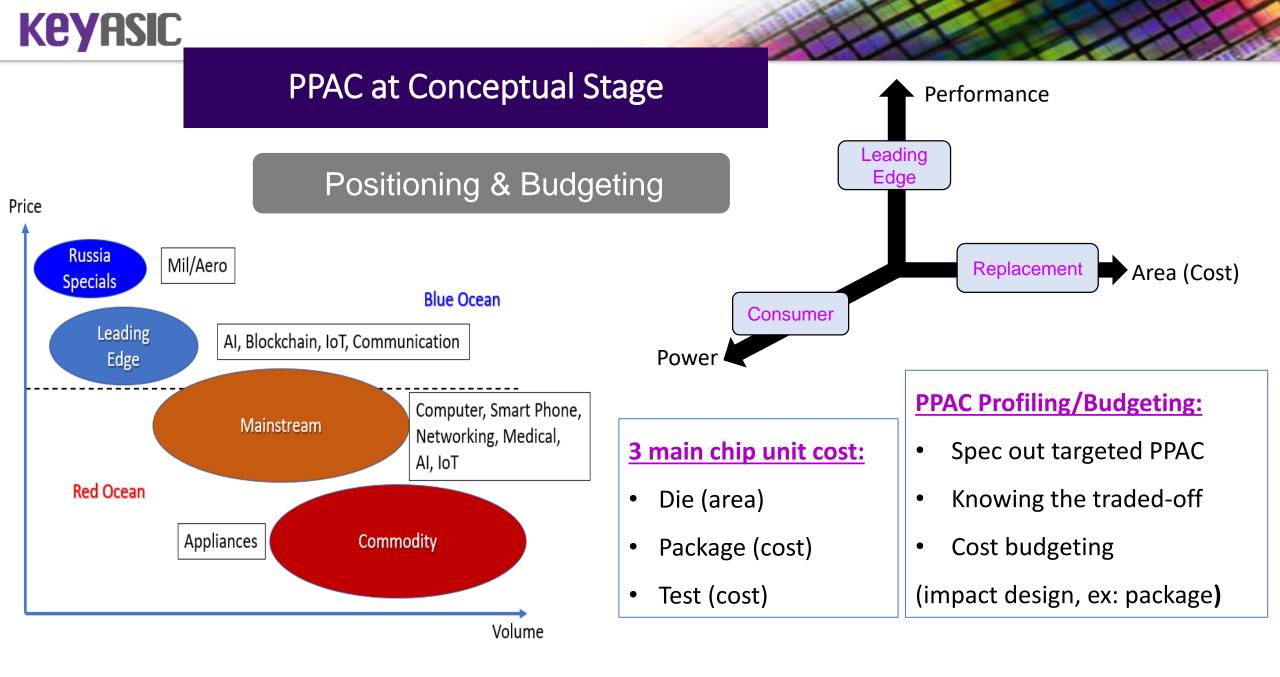

#### Figure of Merit

There are at least 4 important parameters to be considered in

designing & commercializing ASIC/SoC:

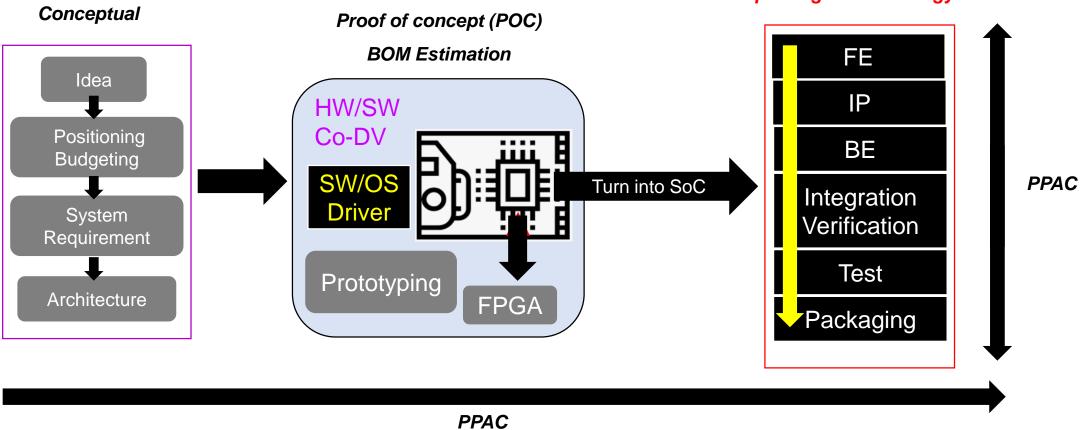

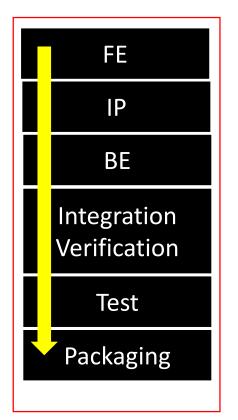

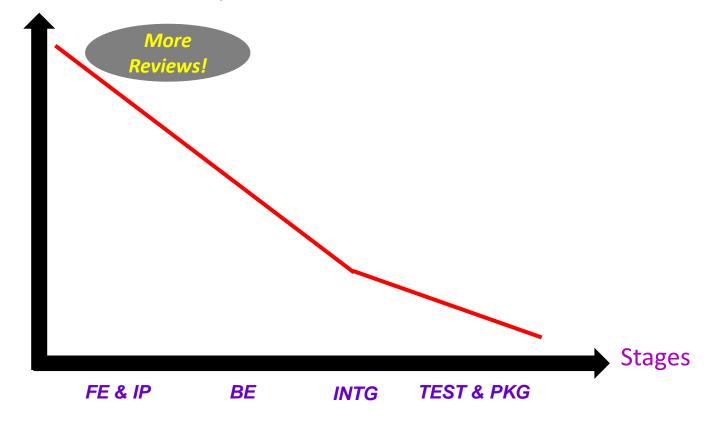

#### **Complete Flow**

Chip Design Methodology

#### POC & HW/SW CO-DV

##

"pre-silicon validation of the embedded system"

- Accelerate SW OS drivers development

- Verify your HW(digital) the earliest

- Simplify HW/SW integration

- Increase real application test coverage

#### FPGA & Prototyping

Choose the right approach based on the complexity

of your chip & the goal of prototyping....

- Standalone FPGA for earliest proof of concept (mostly-digital-based IC)

- FPGA + custom daughters blocks to sign-off major application specific blocks & complex analog IP (Good for multi-chip module or SiP)

- 3. Full custom board to completely verify system (\* HW/SW Co-DV)

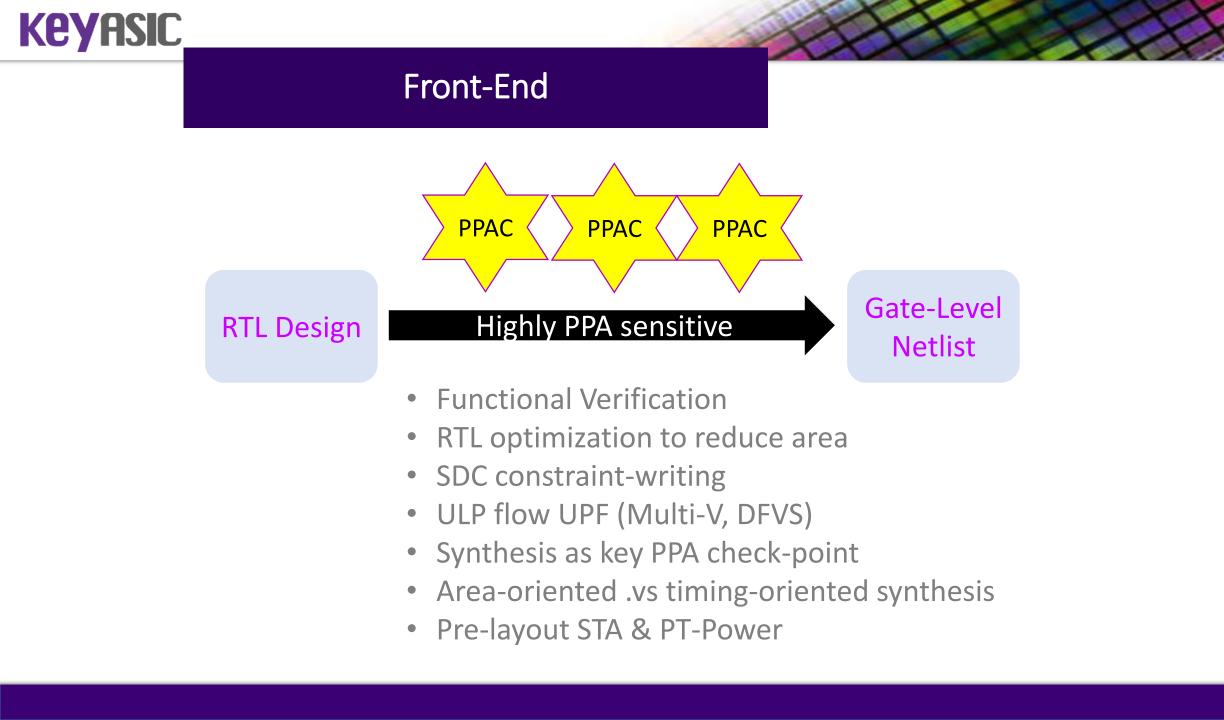

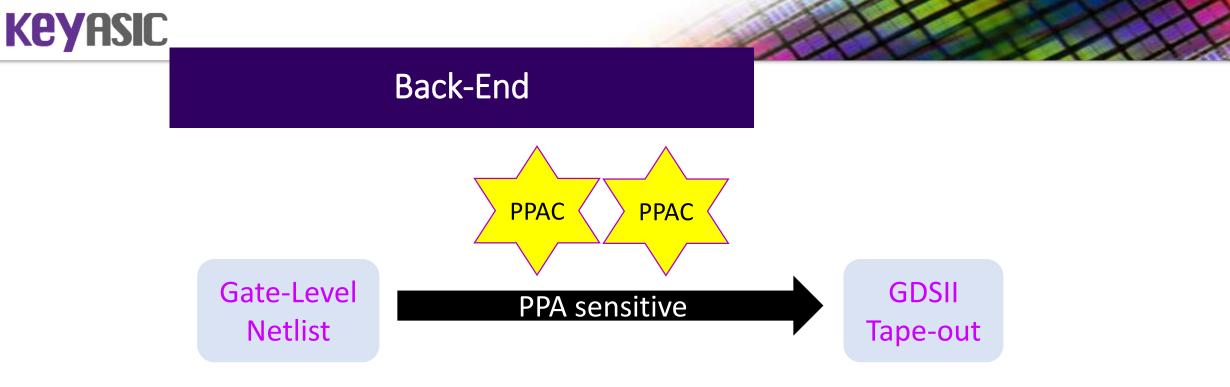

#### Methodology & PPAC

Chip Design Methodology

#### Room for PPAC Optimization

- Physical Design (awareness-based P&R topologies)

- Do not give-in on performance deterioration during P&R

- Master advanced P&R tools & skillset

- ULP SoC segmentation and power routing (Multi-V, DFVS)

- MCMM to optimize design & meet most requirement

- Physical verification

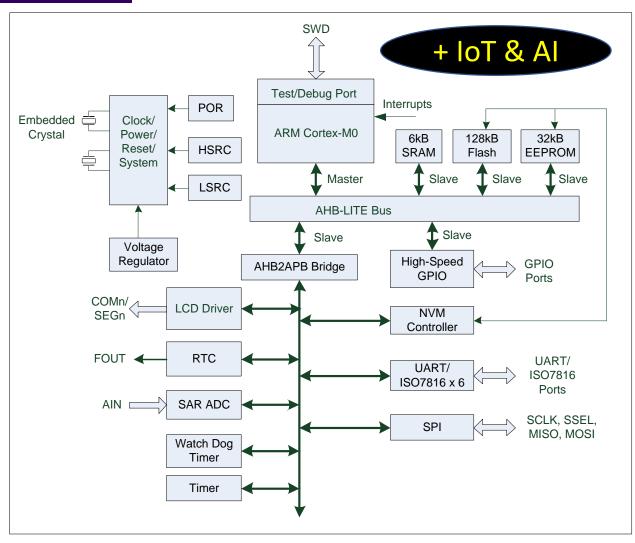

#### Integration & Verification

#### SoC Building Blocks

- Good integration → bring you your targeted PPAC but no extra bonus

- Poor integration → bring you worse PPAC

- Bus architecture, priority bus service (QoS), memory size, power saving mode, data path bottleneck and throughput optimization

- Verification is important to ensure your design function and meet PPA. It should be done at all levels.

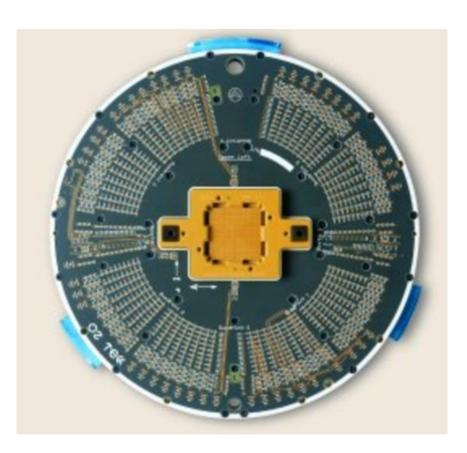

#### Testing & Packaging

- Package Selection

- at least 30% of total unit chip cost

- change chip design to meet the cost (PPAC budgeting)

- IC Testing

- Select the right tester for lower test-time & cost

- Reliability & Compatibility (often overlooked)

- Conduct test at the earliest as it may introduce

unexpected design changes

Common mistakes: start test after few round of MPW tape-out

#### Testing the Reliability

"Losses in the electronics industry have been estimated to range anywhere from half a billion dollars to \$5 billion." – ESDA, 2017

- Cost a business in many different ways

- Total damages of a ruined devices

- Latent defects can have lasting costs tied to efficiency

- Crisis points causing your business to have to postpone product delivery.

#### Scenario

"An ASIC project was delayed for 6 months in production due to latch-up issues. Caused total loss of USD\$400,000."

#### What is the design flow & disciplines?

- ESD/LU circuit design & layout

- I/O padring formation ESD/LU guideline

- Simulate & verify I/O pad-ring in term of ESD/LU

What could possibly went wrong?

- Insufficient ESD design

- I/O design too compact, little spacing for LU

- Violate I/O padring guideline & lack of guard-ring

- Discrepancies with real application (ex: current consumption profile)

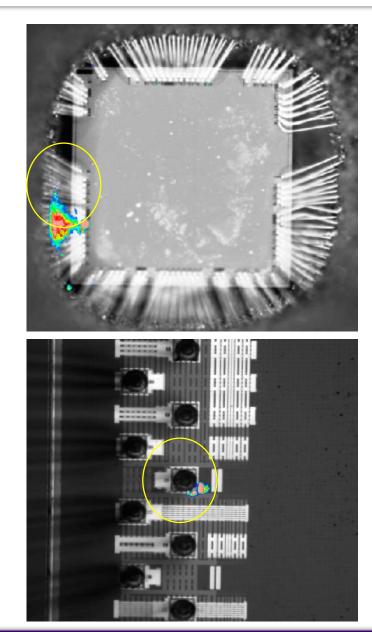

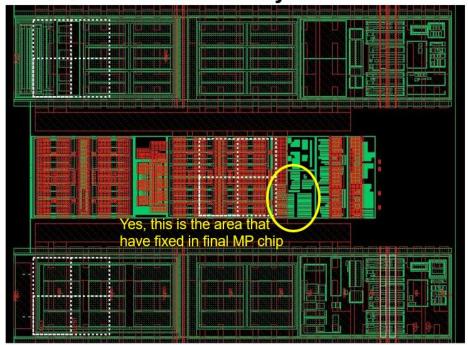

Pin 27 – PAD4 SST18 latched current >> 100mA

0.8X zoom

Pin 27 – PAD4 SST18 layout

- I/O Layout violate LU spacing guideline

- I/O abutment did not follow the proper guideline

Did not follow the good I/O layout practise Lack of methodology to verify (now some already built into DRC) Lack of methodology to govern the formation of I/O padring

- PPAC as the key index to measure how good a chip is

- Besides having the right knowledge & skillset, a competitive design methodology is required

- Execute your flow with disciplines, always check back against PPAC at any stages!

- A chip design methodology outline is presented and will be covered in details in the coming sessions

## Thank You